#### MX-DVA5

## JVC SERVICE MANUAL COMPACT COMPONENT SYSTEM

## **MX-DVA5**

| Area suffix          |  |  |

|----------------------|--|--|

| J U.S.A.<br>C Canada |  |  |

CD / DVD Mechanism is exchanged by a unit (contain CPC cords).

#### Contents

| Safety Precautions1-2            |

|----------------------------------|

| Important for laser products1-3  |

| Preventing static electricity1-4 |

| Importance administering         |

| point on the safety1-5           |

| Disassembly method1       | -6     |

|---------------------------|--------|

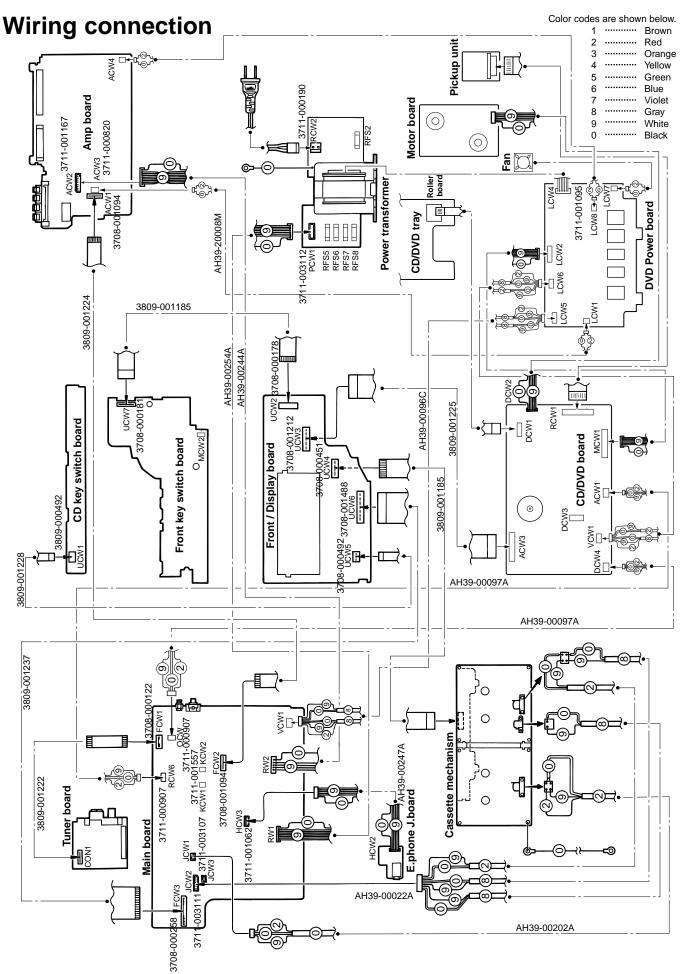

| Wiring connection1        | -18    |

| Adjustment method1        | -19    |

| Troubleshooting1          | -23    |

| Description of major ICs1 | -25~39 |

#### -Safety Precautions

- 1. This design of this product contains special hardware and many circuits and components specially for safety purposes. For continued protection, no changes should be made to the original design unless authorized in writing by the manufacturer. Replacement parts must be identical to those used in the original circuits. Services should be performed by qualified personnel only.

- 2. Alterations of the design or circuitry of the product should not be made. Any design alterations of the product should not be made. Any design alterations or additions will void the manufacturer's warranty and will further relieve the manufacture of responsibility for personal injury or property damage resulting therefrom.

- 3. Many electrical and mechanical parts in the products have special safety-related characteristics. These characteristics are often not evident from visual inspection nor can the protection afforded by them necessarily be obtained by using replacement components rated for higher voltage, wattage, etc. Replacement parts which have these special safety characteristics are identified in the Parts List of Service Manual. Electrical components having such features are identified by shading on the schematics and by (<sup>(A)</sup>) on the Parts List in the Service Manual. The use of a substitute replacement which does not have the same safety characteristics as the recommended replacement parts shown in the Parts List of Service Manual may create shock, fire, or other hazards.

- 4. The leads in the products are routed and dressed with ties, clamps, tubings, barriers and the like to be separated from live parts, high temperature parts, moving parts and/or sharp edges for the prevention of electric shock and fire hazard. When service is required, the original lead routing and dress should be observed, and it should be confirmed that they have been returned to normal, after re-assembling.

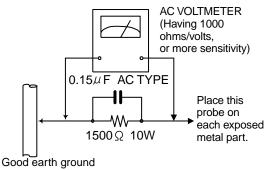

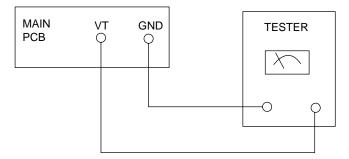

- 5. Leakage currnet check (Electrical shock hazard testing)

After re-assembling the product, always perform an isolation check on the exposed metal parts of the product (antenna terminals, knobs, metal cabinet, screw heads, headphone jack, control shafts, etc.) to be sure the product is safe to operate without danger of electrical shock.

Do not use a line isolation transformer during this check.

Plug the AC line cord directly into the AC outlet. Using a "Leakage Current Tester", measure the leakage current from each exposed metal parts of the cabinet, particularly any exposed metal part having a return path to the chassis, to a known good earth ground. Any leakage current must not exceed 0.5mA AC (r.m.s.).

#### Alternate check method

Plug the AC line cord directly into the AC outlet. Use an AC voltmeter having, 1,000 ohms per volt or more sensitivity in the following manner. Connect a 1,500  $\Omega$  10W resistor paralleled by a 0.15 $\mu$ F AC-type capacitor

between an exposed metal part and a known good earth ground. Measure the AC voltage across the resistor with the AC voltmeter.

Move the resistor connection to each exposed metal part, particularly any exposed metal part having a return path to the chassis, and meausre the AC voltage across the resistor. Now, reverse the plug in the AC outlet and repeat each measurement. Voltage measured any must not exceed 0.75 V AC (r.m.s.). This corresponds to 0.5 mA AC (r.m.s.).

#### Warning

- 1. This equipment has been designed and manufactured to meet international safety standards.

- 2. It is the legal responsibility of the repairer to ensure that these safety standards are maintained.

- 3. Repairs must be made in accordance with the relevant safety standards.

- 4. It is essential that safety critical components are replaced by approved parts.

- 5. If mains voltage selector is provided, check setting for local voltage.

In regard with component parts appearing on the silk-screen printed side (parts side) of the PWB diagrams, the parts that are printed over with black such as the resistor (-), diode (+) and ICP (-) or identified by the " $\underline{\Lambda}$ " mark nearby are critical for safety.

(This regulation does not correspond to J and C version.)

Burrs formed during molding may be left over on some parts of the chassis. Therefore, pay attention to such burrs in the case of preforming repair of this system

#### Important for laser products

#### **1.CLASS 1 LASER PRODUCT**

- **2.DANGER :** Invisible laser radiation when open and inter lock failed or defeated. Avoid direct exposure to beam.

- **3.CAUTION :** There are no serviceable parts inside the Laser Unit. Do not disassemble the Laser Unit. Replace the complete Laser Unit if it malfunctions.

- **4.CAUTION :** The compact disc player uses invisible laserradiation and is equipped with safety switches whichprevent emission of radiation when the drawer is open and the safety interlocks have failed or are de feated. It is dangerous to defeat the safety switches.

- **5.CAUTION :** If safety switches malfunction, the laser is able to function.

- **6.CAUTION :** Use of controls, adjustments or performance of procedures other than those specified herein may result in hazardous radiation exposure.

A CAUTION Please use enough caution not to see the beam directly or touch it in case of an adjustment or operation check.

#### **Reproduction and position of labels** CLASS 1 LASER PRODUCT WARNING LABEL CLASS 1 LASER PRODUCT CAUTION: INVISIBLE LASER RADIATION WHEN OPEN AND INTERLOCKS DEFEATED AVOID EXPOSURE TO BEAM KLASSE 1 LASER PRODUKT LUOKAN 1 LASER LAITE ADVARSAL: USYNLIG LASERSTRALING VEO ABNING NAR SIKKERHEDSAFBRYDERE ER UDE AF FUNKTION UNDGA UDSAFTTELSE FOR STRALING KLASS 1 LASER APPARAT PRODUCTO LASER CLASE VARO:AVATTAESSA JA SUOJALUKITUS OHITETAESSA OLET ALTTINA NAKYMATTOMALLELASERSATEILYLLE ALA KATSO SATEESEENI VARNING:OSYNLIG LASERSTRALNING NAR DEN DEL AR OPPNAD OCH SPARREN AR URKOPPLAD BETRAKTA FLISTEN ш 22 610 639

#### **Preventing static electricity**

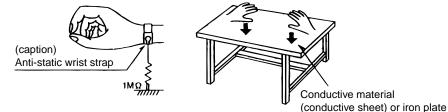

#### 1. Grounding to prevent damage by static electricity

Electrostatic discharge (ESD), which occurs when static electricity stored in the body, fabric, etc. is discharged, can destroy the laser diode in the traverse unit (optical pickup). Take care to prevent this when performing repairs.

#### 2. About the earth processing for the destruction prevention by static electricity

In the equipment which uses optical pick-up (laser diode), optical pick-up is destroyed by the static electricity of the work environment.

Be careful to use proper grounding in the area where repairs are being performed.

#### 2-1 Ground the workbench

Ground the workbench by laying conductive material (such as a conductive sheet) or an iron plate over it before placing the traverse unit (optical pickup) on it.

#### 2-2 Ground yourself

Use an anti-static wrist strap to release any static electricity built up in your body.

#### 3. Handling the optical pickup

- 1. In order to maintain quality during transport and before installation, both sides of the laser diode on the replacement optical pickup are shorted. After replacement, return the shorted parts to their original condition. (Refer to the text.)

- 2. Do not use a tester to check the condition of the laser diode in the optical pickup. The tester's internal power source can easily destroy the laser diode.

#### 4. Handling the traverse unit (optical pickup)

- 1. Do not subject the traverse unit (optical pickup) to strong shocks, as it is a sensitive, complex unit.

- 2. Cut off the shorted part of the flexible cable using nippers, etc. after replacing the optical pickup. For specific details, refer to the replacement procedure in the text. Remove the anti-static pin when replacing the traverse unit. Be careful not to take too long a time when attaching it to the connector.

- 3. Handle the flexible cable carefully as it may break when subjected to strong force.

- 4. It is not possible to adjust the semi-fixed resistor that adjusts the laser power. Do not turn it.

#### Attention when traverse unit is decomposed

Because the CD / DVD mechanism assembly of this model is a unit component, the individual component parts consisting of the CD / DVD mechanism assembly are not supplied separately.

If you need to decompose the traverse unit, short-circuit the connector of the flexible board by using a metal clip and the like prior to decomposing the traverse unit.

#### Importance administering point on the safety

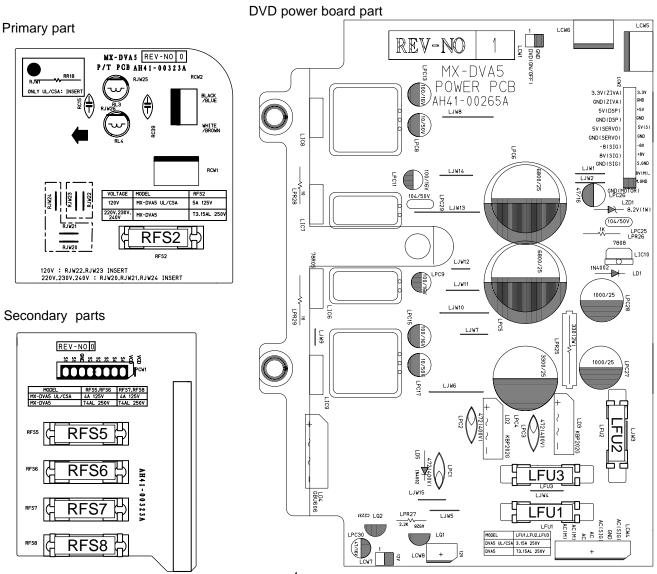

For USA and Canada / pour États - Unis d' Amérique et Canada

Caution: For continued protection against risk of fire, replace only with same type 5A/125V for RFS2, 4A/125V for RFS5,RFS6,RFS7, and RFS8, 3.15A /250V for LFU1,LFU2, and LFU3. This symbol specifies type of fast operating fuse.

Précaution: Pour eviter risques de feux, remplacez le fusible de sureté de RFS2 comme le meme type que 5A/125V, et 4A/125V pour RFS5,RFS6,RFS7, et RFS8, 3.15A /250V for LFU1,LFU2, and LFU3. Ce sont des fusibles sûretes qui functionnes rapide.

#### **Disassembly method**

#### <Main body>

#### Removing the metal cover

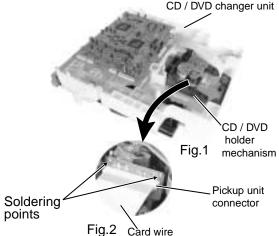

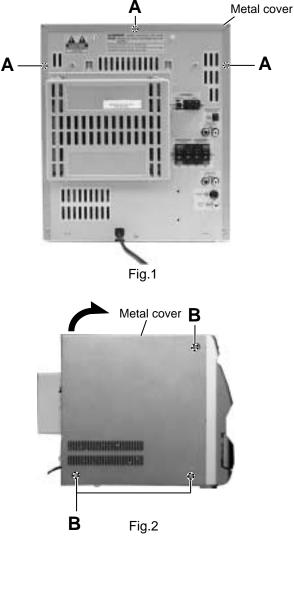

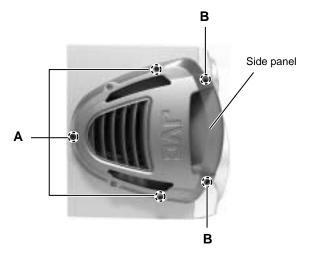

(See Fig.1 and 2)

- 1. Remove the three screws **A** attaching the metal cover on the back of the body.

- 2. Remove the six screws **B** attaching the metal cover on both sides of the body.

- 3. Remove the metal cover from the body by lifting the rear part of the cover.

- ATTENTION: Do not break the front panel tab fitted to the metal cover.

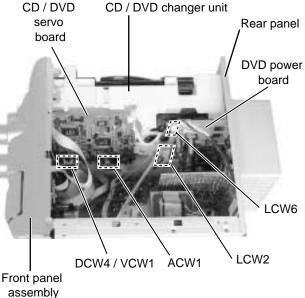

- Prior to performing the following procedure, remove the metal cover.

- 1. Disconnect the card wire which is attached with adhesive to the left side of the CD / DVD changer unit.

- 2. Disconnect the harness from connector ACW1,DCW4 and VCW1 of the CD / DVD servo board on the back of the CD / DVD changer unit.

- 3. Disconnect the harness from connector LCW2 and LCW6 on the DVD power board.

- 4. Disconnect the card wire from connector UCW3 on the FL dispaly & System control board.

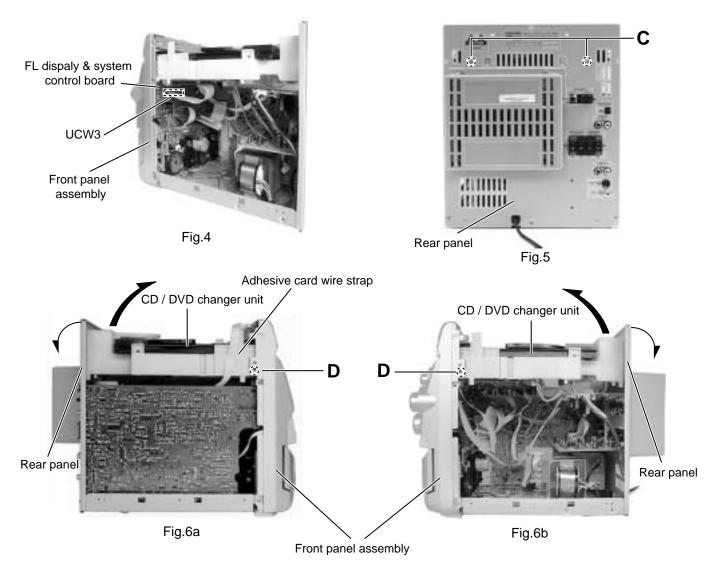

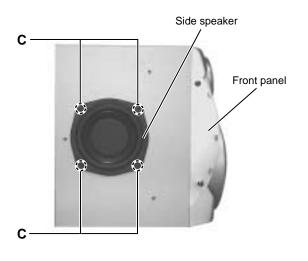

- 5. Remove the two screws **C** attaching the CD / DVD changer unit on the back of the body.

- 6. Remove the two screws **D** attaching the CD / DVD changer unit on the both side of the body.

- 7. Draw the CD / DVD changer unit upward from behind while pulling the rear panel outward.

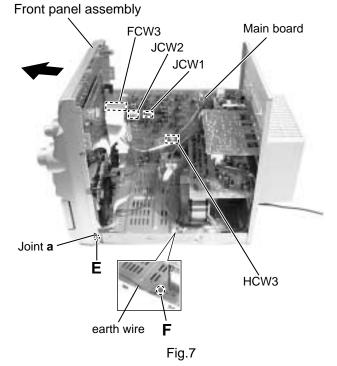

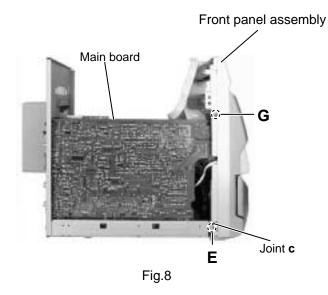

#### Removing the front panel assembly (See Fig.7 to 9)

- Prior to performing the following procedure, remove the metal cover and the CD / DVD changer unit.

- 1. Disconnect the card wire from connector FCW3 and the harness from connector JCW1, JCW2 and HCW3 on the inner side of the main board in the body.

- 2. Remove the two screws **E** attaching the front panel assembly on both sides of the body.

- 3. Remove the screw **F** attaching the earth terminal extending from the cassette mechanism assembly.

- 4. Remove the screw **G** attaching the front panel assembly and main board.

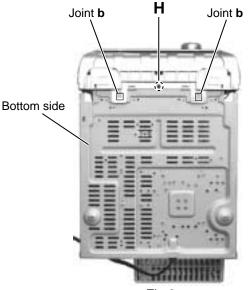

- 5. Remove the screw **H** attaching the front panel assembly on the bottom of the body.

- Release the two joints a on both sides and two joints

b on the bottom of the body using a screwdriver.

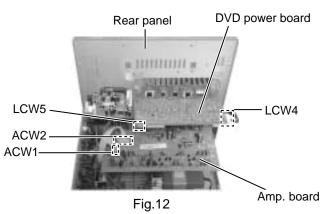

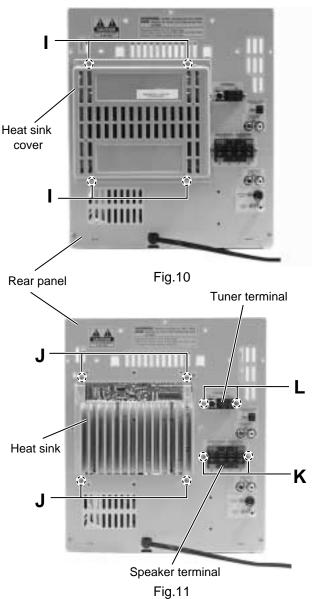

#### Removing the heat sink, amp. board and DVD power board (See Fig.10 to 12)

- Prior to performing the following procedure, remove the metal cover and the CD / DVD changer unit.

- 1. Remove the four screws I attaching the heat sink cover on the back of the body. Remove the heat sink cover.

- 2. Remove the four screws **J** attaching the heat sink, amp. board and DVD power board to the rear panel on the back of the body.

- 3. Remove the two screws **K** attaching the speaker terminal to the rear panel on the back of the body.

- 4. Disconnect the card wire from connector ACW1 and the harness from connector ACW2 on the amp. board.

- 5. Disconnect the harness from connector LCW5 and LCW4 on the DVD power board.

- 6. After moving the heat sink upward, remove the claws. Then pull out the heat sink, amp. board and DVD power board inward.

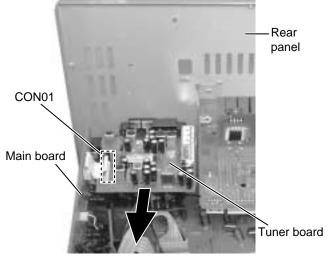

#### ■Removing the tuner board (See Fig.11 and 13)

- Prior to performing the following procedure, remove the metal cover and CD / DVD changer unit.

- 1. Disconnect the card wire from connector CON01 on the tuner board.

- 2. Remove the two screws  ${\boldsymbol{\mathsf{L}}}$  attaching the tuner board.

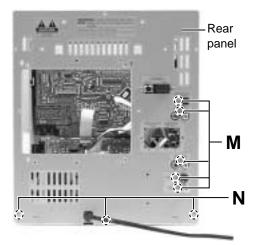

#### ■ Removing the rear panel (See Fig.14)

- Prior to performing the following procedure, remove the metal cover, CD / DVD changer unit, heat sink & Amp. board and tuner board.

- 1. Remove the three screws **N** and five screws **M** attaching the rear panel.

Fig.14

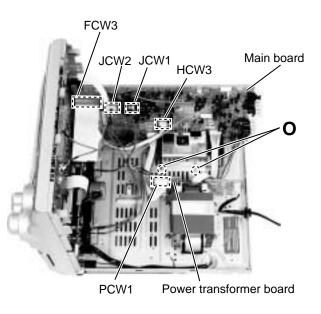

#### Removing the main Board

(See Fig. 15)

- Prior to performing the following procedure, remove the metal cover, CD / DVD changer unit, heat sink & Amp. board tuner board and rear panel.

- 1. Disconnect the card wire from connector FCW3 and the harness from connector JCW1, JCW2, and HCW3 on the main board.

- 2. Disconnect the harness from connector PCW1 on the power transformer board.

- 3. Remove the screw **G** attaching the main board holder. (See Fig.8)

- 4. Remove the two screws **O** attaching the heat sink and bottom chassis.

Fig.15

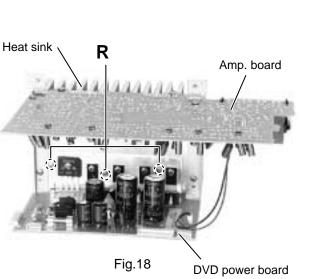

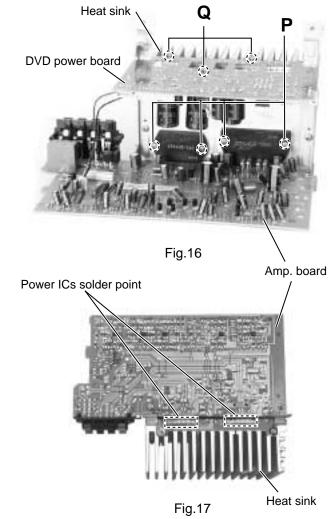

#### Removing the power ICs and DVD power board (See Fig.16 to 18)

- Prior to performing the following procedure, remove the metal cover, CD / DVD changer unit, heat sink, amp. board and DVD power board.

- 1. Remove the four screws **P** attaching the power ICs to the heat sink.

- 2. Unsolder the power ICs solder point.

- 3. Remove the three screws **Q** and three screws **R** attaching the DVD power board to the heat sink.

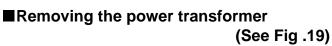

- Prior to performing the following procedure, remove the metal cover, CD / DVD changer unit, heat sink & Amp. board, tuner board and rear panel.

- 1. Disconnect the power cord from connector RCW2 of the power transformer board.

- 2. Disconnect the harness from connector PCW1 of the power transformer board.

- 3. Remove the four screws **S** attaching the power transformer.

#### <Front panel assembly>

• Prior to performing the following procedure, remove the metal cover, the CD / DVD changer unit and the front panel assembly.

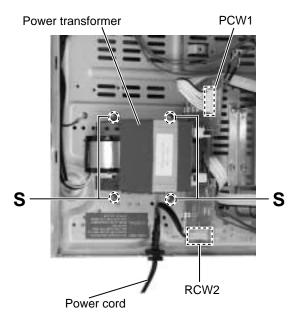

#### Removing the power / DVD switch board (See Fig.20)

- 1. Disconnect the card wire from connector UCW1 of the power / DVD switch board.

- 2. Remove the five screws **T** attaching the power / DVD switch board and release the tab **c** outward.

#### Removing the FL display & System control board (See Fig.20)

- Disconnect the card wire from the connector UCW3, UCW4,UCW5 and UCW6 on the FL display & System control board.

- Remove the five screws U attaching the FL display & System board.

- 3. Disconnect the card wire from the connector UCW2 on the FL display & System control board.

#### Removing the headphone board

(See Fig.21)

- Prior to performing the following procedure remove the FL display & System control board.

- 1. You can pull out the headphone board.

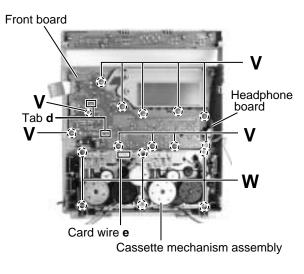

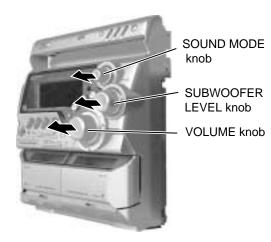

#### Removing the front board (See Fig. 21 and 22)

- Prior to performing the following procedure, remove the FL display & System control board.

- 1. Pull out the volume knob, subwoofer level knob and sound mode nob from front side.

- 2. Remove the eleven screws V attaching the front board and release the two tabs d outward.

### Removing the cassette mechanism assembly (See Fig.21)

- 1. Disconnect the card wire **e** from the mechanism board on the cassette mechanism assembly.

- 2. Remove the six screws **W** attaching the cassette mechanism assembly.

Fig.21

Fig.22

#### MX-DVA5

#### <CD / DVD changer unit>

· Prior to performing the following procedure, remove the CD / DVD changer unit.

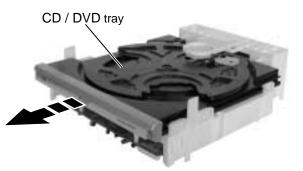

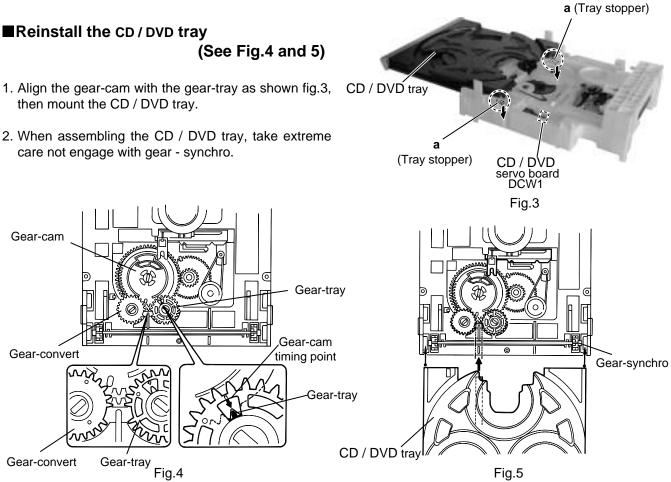

#### ■Removing the CD / DVD tray (See Fig.1 to 3)

- 1. Disconnect the card wire from connector RCW1 of the CD /DVD servo board.

- 2. Turn the black loading pulley gear on the under side of the CD / DVD changer unit in the direction of the arrow and draw the CD / DVD tray toward the front until it stops.

- 3. Disconnect the card wire from connector DCW1 of the CD / DVD servo board on the upper side of the CD / DVD changer unit.

- 4. Push down the two tray stoppers marked a and pull out the CD / DVD tray.

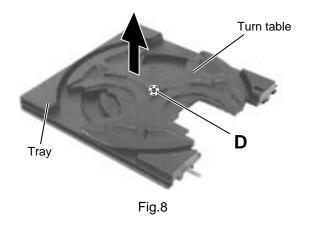

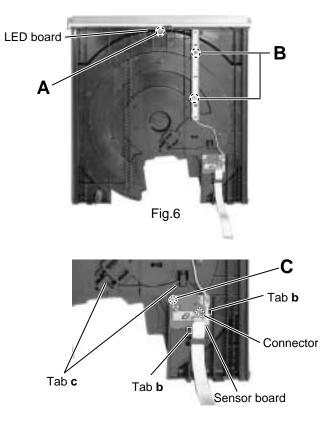

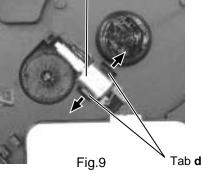

## Removing the sensor board, the LED board and the turn table motor assembly (See Fig.6 to 9)

- Prior to performing the following procedure, remove the CD / DVD tray.

- 1. Remove the screw **A** attaching the LED board and release the screws **B** attaching the bracket.

- 2. Remove the screw **C** attaching the sensor board and release the two tabs **b** attaching the sensor board on the under side of the CD / DVD tray.

- 3. Disconnect the harness from connector on the sensor board and release the harness from the two hooks **c**. Remove the sensor board.

- 4. Remove the screw **D** attaching the turn table. Detach the turn table from the tray.

- 5. Pull outward the tab marked **d** attaching the turn table motor assembly on the upper side of the tray and detach the turn table motor assembly from the tray.

Fig.7

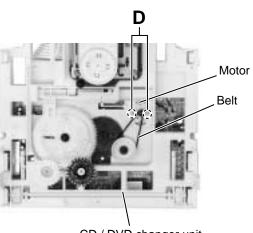

#### ■Removing the belt, and the motor (See Fig.10)

- Prior to performing the following procedure, remove the CD / DVD tray.

- 1. Detach the belt from the pulley on the upper side of the CD / DVD changer unit (Do not stain the belt with grease).

- 2. Remove the two screws **D** attaching the motor.

CD / DVD changer unit Fig.10

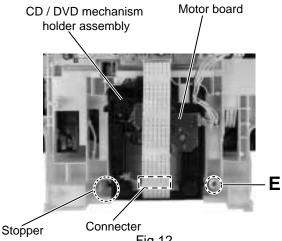

#### ■Removing the CD / DVD servo board (See Fig. 12)

- Prior to performing the following procedure, remove the CD / DVD tray, the two screws attaching the motor and detach the belt from the pulley.

- 1. Unsolder points the motor terminal.

- 2. Disconnect the card wire from the connector RCW1 on the CD / DVD servo board.

- 3. Disconnect the motor board wire from the motor board connector on the motor board.

- 4. Remove the three screws **D** attaching the CD / DVD servo board.

## CD / DVD servo board Solder points

Fig.11

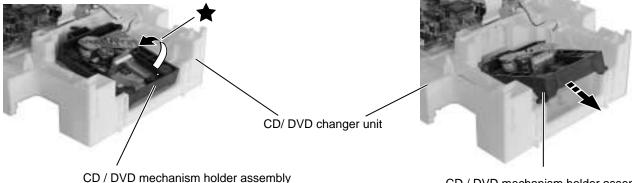

#### Removing the CD / DVD mechanism holder assembly (mechanism included) (See Fig.12 to 14)

- Disconnect the motor wire from connector on the motor board in the CD / DVD mechanism holder assembly on the under side of the CD / DVD changer unit.

- Disconnect the card wire from connector on the pickup unit in the CD / DVD mechanism holder assembly.

- 3. Remove the screw **E** attaching the shaft on the right side of the CD / DVD mechanism holder assembly.

- Pull outward the stopper fixing the shaft on the left side and remove the CD / DVD mechanism holder assembly from behind in the direction of the arrow ★.

- 5. Pull out the CD / DVD mechanism holder assembly.

/ DVD mechanism holder as

CD / DVD mechanism holder assembly

#### <Cassette mechanism section>

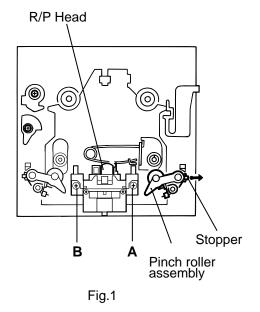

• Removing the record/playback mechanism.

#### ■ Removing the R/P head.

- Remove the screw A on the right side of the R/P head.(Fig.1)

- 2. Remove the screw **B** on the left side of the R/P head.(Fig.1)

#### Removing the pinch roller.

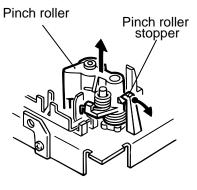

- 1. Pull out the pinch roller by opening the pinch roller stopper outward to unlock .(Fig.2)

- 2. When reassembling the pinch roller, refer to fig. 3 to hook up the spring.

Fig.2

Fig.3

#### MX-DVA5

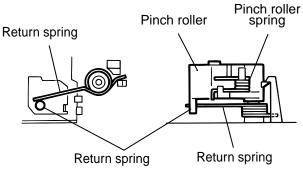

#### Removing the motor.

- Remove the two screws C fixing the motor. Be careful to grease's splash when the drive belt comes off.(Fig.4, Fig.5)

- 2. Unsolder the motor terminal.(Fig.4)

#### Removing the mechanism board.

- 1. Unsolder the four parts **a** on the solenoid coil terminal.(Fig.4)

- 2. Remove the two screws  $\mathbf{D}$  fixing the board.(Fig.4)

- 3. Unhook the three parts **b** from the board.(Fig.4)

- 4. Remove the mechanism board.(Fig.4)

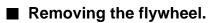

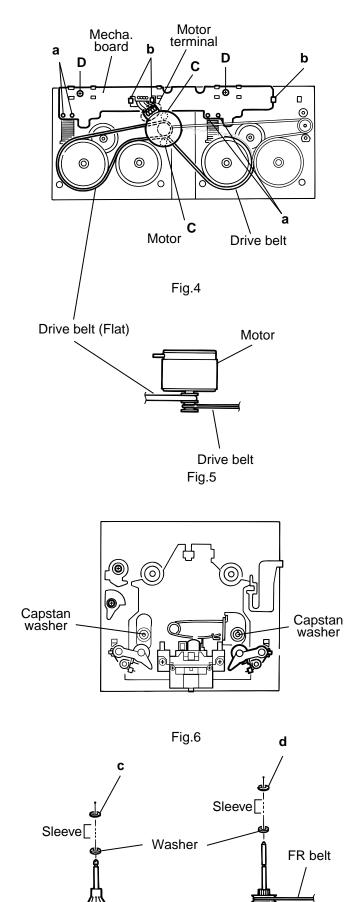

Remove the cut-washers at **c** and **d** from the capstan shaft, then remove the flywheel. When reassembling the flywheel, be sure to use new washers as they cannot be reused. (Fig.7, Fig.8)

Flywheel

FR belt

Fig.7

Flywheel

Flywheel

#### < Speaker section >

#### Removing the side panel (See Fig. 1)

1. Remove the five screws **A** and **B** attaching the side panel, then remove the side panel.

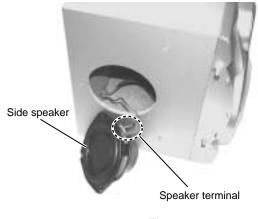

#### Removing the side speaker

(See Fig. 2 and 3)

Prior to performing the following procedure, remove the side panel.

- 1. Remove the fore screws **C** attaching the side speaker.

- 2. Pull out the side speaker and remove the speaker cord from the speaker terminal.

Fig.2

Fig.3

#### Adjustment method

1. Tuner

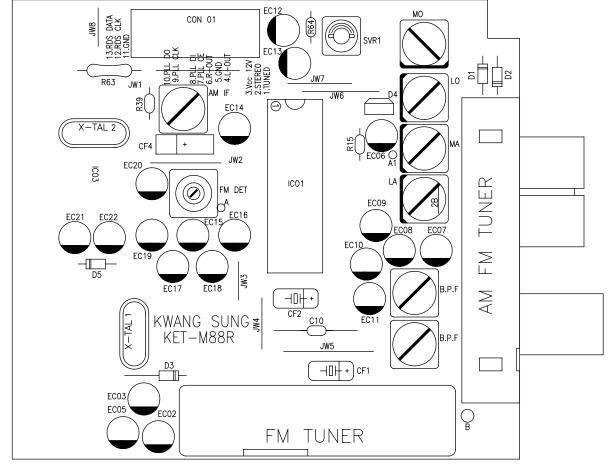

\* Adjustment Location of Tuner PCB

| ITEAM               | AM(MW) OSC<br>Adjustment | AM(MW) RF<br>Adjustment   |  |

|---------------------|--------------------------|---------------------------|--|

| Received FREQ.      | 530~1710 KHz             | 600 KHz                   |  |

| Adjustment<br>point | МО                       | MA                        |  |

| Output              | 1~7.0 V                  | Maximum<br>Output(Fig1-4) |  |

Fig 1-4 OSC Voltage

#### MX-DVA5

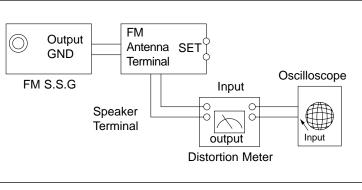

| FM THD Adjustment                               |                  |  |  |  |

|-------------------------------------------------|------------------|--|--|--|

| SSG FREQ.                                       | 98 MHz           |  |  |  |

| Adjustment<br>point<br>(FM DET)                 | FM DETECTOR COIL |  |  |  |

| Output                                          | 60 dB            |  |  |  |

| Minumum Distortion (0.4% below)<br>(Figure 1-1) |                  |  |  |  |

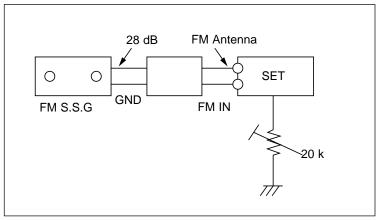

| FM Search Level Adjustment                                  |                                       |  |  |  |

|-------------------------------------------------------------|---------------------------------------|--|--|--|

| SSG FREQ.                                                   | 98 MHz                                |  |  |  |

| Adjustment<br>point<br>(SVR1)                               | BEACON<br>SENSITIVITY<br>SEMI-VR(20K) |  |  |  |

| Output                                                      | 28 dB                                 |  |  |  |

| Adjust SVR1 so that "TUNED" of FL T is lighted (Figure 1-2) |                                       |  |  |  |

| *Adjust FM S.S.G level to 28dB                              |                                       |  |  |  |

Figure1-2 FM Auto Search Level Adjustment

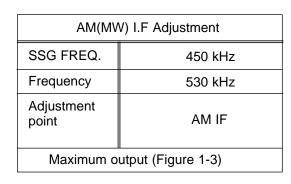

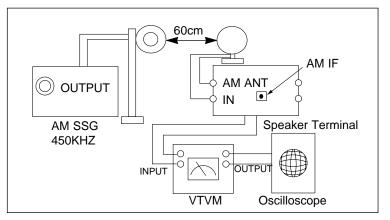

Figure1-3 AM I.F Adjustment

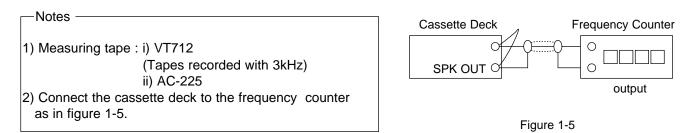

#### 2 Cassette Deck

#### 2-1 To Adjust Tape Speed

| Step | ltem                     | Pre-Setup<br>Condition                            | Pre-Setup                                                                                                     | To Adjust                                       | Standard   | Remark |

|------|--------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------|--------|

| 1    | TAPE<br>SPEED<br>Control | OUT<br>(connected<br>to the frequency<br>counter) | <ol> <li>1) Deck 1:VT712</li> <li>2) Press PLAY<br/>SW button</li> <li>3) Deck 2:Same<br/>as above</li> </ol> | Turn USR1 to<br>left and right<br>(FRONT board) | 3KHz ±30Hz |        |

Figure 1-8

#### 2-2 To Adjust Playback Level / REC

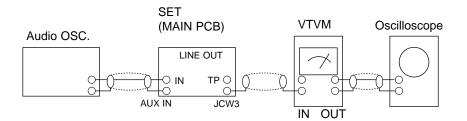

# Notes 1) Before the actual adjustment, clean the play/recording head. 2) Measuring tape : i) VT-703 (10kHz AZIMUTH control) ii) AC-225 iii) VT-724 (1kHz Reference level) 3) The cassette deck is connections as shown in figure 1-7.

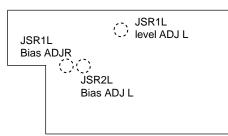

## Arrangement of adjusting positions

Main board section (Foward side)

Figure. 1-9

#### 1. Adjust Deck A Play Level

| Step | ltem    | Pre-Setup<br>Condition                            | Pre-Setup                                                                                            | To Adjust                                               | Standard                                        | Remark                                                                                                    |

|------|---------|---------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

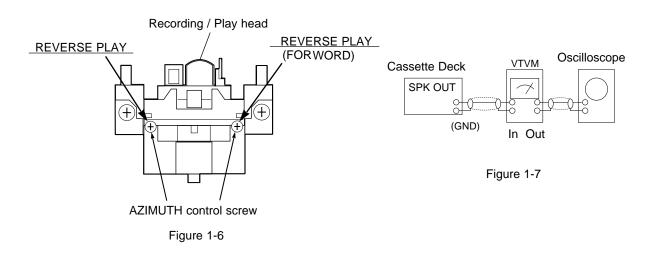

| 1    | AZIMUTH | SPK OUT<br>(VTVM is<br>connected to<br>the scope) | After putting VT-<br>703 into Deck A<br>1) Press FWD PLAY<br>button.<br>2) Press RVS PLAY<br>button. | Turn the control<br>screw to as shown<br>in Figure 1-6. | Max output<br>and same phase<br>(both channels) | After adjustment<br>secure it with<br>REGION LOCK.<br>Adjust AZIMUTH<br>when you<br>exchange the<br>head. |

#### 2. Adjust Deck B Play Level / REC BIAS

| Step | ltem                         | Pre-Setup<br>Condition                            | Pre-Setup                                                                                                        | To Adjust                                               | Standard                                                                             | Remark                                                                                                    |

|------|------------------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 1    | AZIMUTH                      | SPK OUT<br>(VTVM is<br>connected to<br>the scope) | After putting VT-<br>703 into Deck B<br>1)Press FWD PLAY<br>button.<br>2)Press RVS PLAY<br>button.               | Turn the control<br>screw to as shown<br>in Figure 1-6. | Max output<br>and same phase<br>(both channels)                                      | After adjustment<br>secure it with<br>REGION LOCK.<br>Adjust AZIMUTH<br>when you<br>exchange the<br>head. |

| 2    | Recording<br>Bias<br>Voltage | Fig 1-8                                           | After putting AC-<br>225 into Deck B<br>1) Press REC PLAY<br>button.<br>2) MAIN board JCW3,<br>connected to VTVM | Turn JSR2L,JSR2R<br>to the right and left               | 7mV                                                                                  |                                                                                                           |

| 3    | Reference<br>level           | SPK OUT<br>(VTVM is<br>connected to<br>the scope) | After putting VT-724<br>into Deck B<br>Press PLAY button.                                                        | Turn JSR1L to the right and left Figure 1-7,1-9.        | Output of the left<br>channel is<br>combined in the<br>level of the right<br>channel |                                                                                                           |

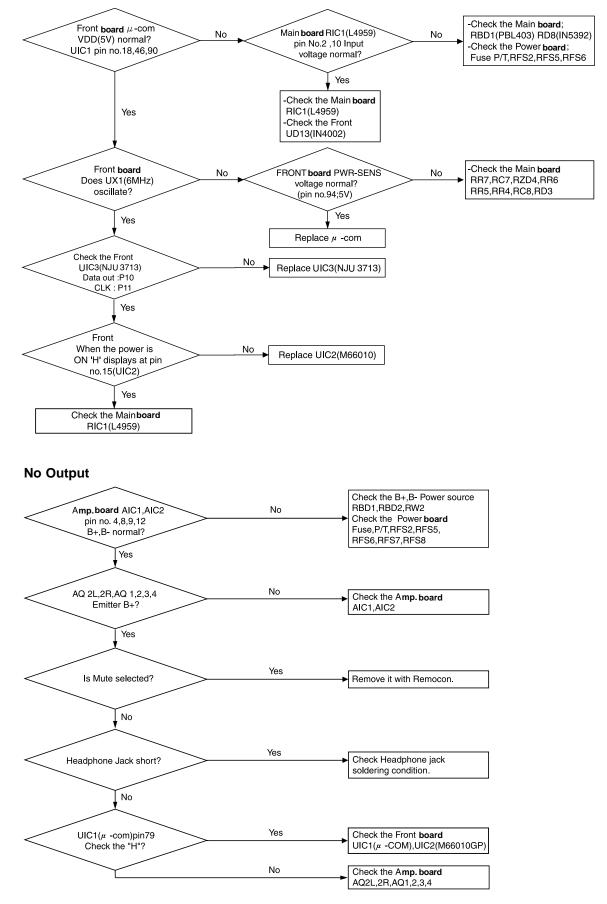

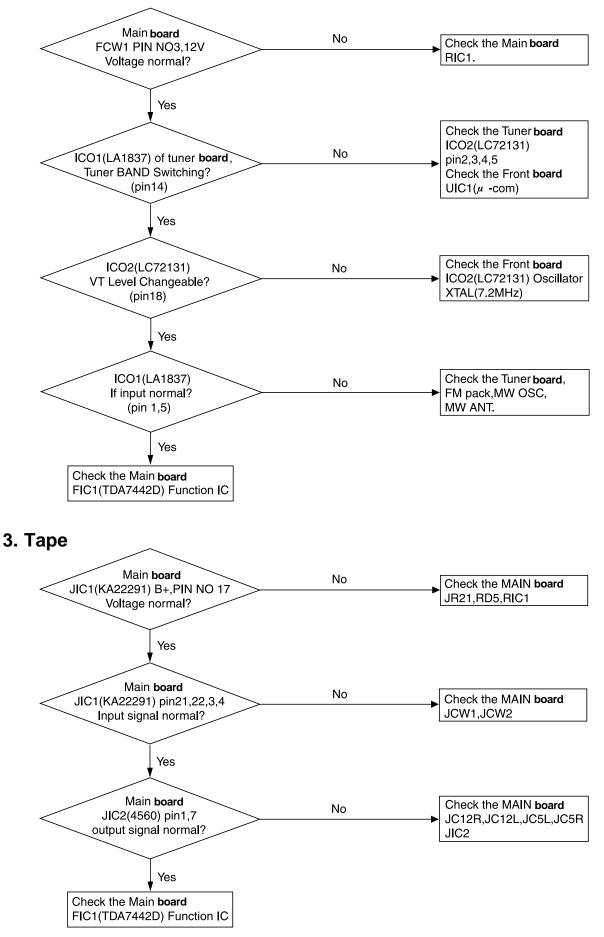

#### Troubleshooting

#### 1. Amplifier

#### 2. Tuner Malfunction (FM/AM)

#### **Description of major ICs**

■ 74HCU04 (OIC1) : Optical

1.Pin layout

| 2A3     126Y       2Y4     04U     1115A       3A5     105Y       3Y6     94A       GND7     84Y | 2Y 4<br>3A 5<br>3Y 6 | 04U | 105Y<br>94A |

|--------------------------------------------------------------------------------------------------|----------------------|-----|-------------|

|--------------------------------------------------------------------------------------------------|----------------------|-----|-------------|

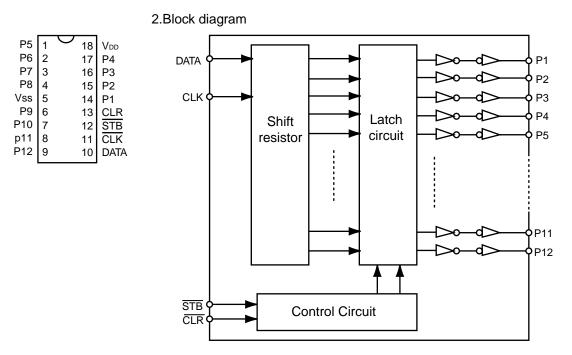

#### ■ NJU3713 (UIC3) : L.E.D. driver

1.Pin layout

#### 3.Pin function

| PIN No. | I/O | Symbol            | Function                                  |

|---------|-----|-------------------|-------------------------------------------|

| 1~4     | 0   | P5, P6, P7, P8    | Parallel conversion data output terminal. |

| 5       | -   | Vss               | Connect to GND.                           |

| 6~9     | 0   | P9, P10, P11, P12 | Parallel conversion data output terminal. |

| 10      | 0   | DATA              | Serial data input terminal.               |

| 11      | Ι   | CLK               | Clock signal input terminal.              |

| 12      | Ι   | STB               | Strobe signal input terminal.             |

| 13      | Ι   | CLR               | Clear signal input terminal.              |

| 14      | 0   | P1                | Parallel conversion data output terminal. |

| 15      | 0   | P2                | Parallel conversion data output terminal. |

| 16~17   | 0   | P3, p4,           | Parallel conversion data output terminal. |

| 18      | -   | Vdd               | Power supply terminal.                    |

#### MX-DVA5

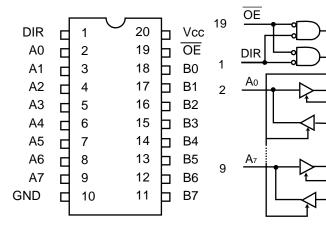

#### ■ 74HCT245 (U15) : Octal bus transceiver; 3-state

2. Block diagram

| Inputs |     | Inputs Inputs / output |        |

|--------|-----|------------------------|--------|

| OE     | DIR | An                     | Bn     |

| L      | L   | A = B                  | inputs |

| L      | Н   | inputs                 | B = A  |

| Н      | Х   | Z                      | Z      |

1. H = High voltage level

L = Low voltage level

X = don't care

Z = high impedance OFF - state

3.Pin function

| Pin No.                        | I/O | Symbol | Function                           |

|--------------------------------|-----|--------|------------------------------------|

| 1                              | -   | DIR    | Direction control                  |

| 2, 3, 4, 5, 6, 7, 8, 9         | I/O | A0 ~A7 | Data inputs / outputs              |

| 10                             | -   | GND    | Ground                             |

| 18, 17, 16, 15, 14, 13, 12, 11 | I/O | B0~B7  | Data inputs / outputs              |

| 19                             | I/O | OE     | Outputs enable inputs (active LOW) |

| 20                             | -   | Vcc    | positive supply voltage            |

<u></u>∎₀ - 18

B7 - 11

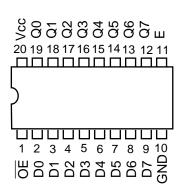

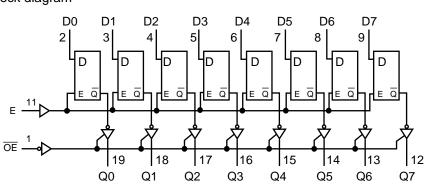

#### ■ 74LVT573 (U10, 11, 12) : Logic / flip flop

1. pin layout

2. Block diagram

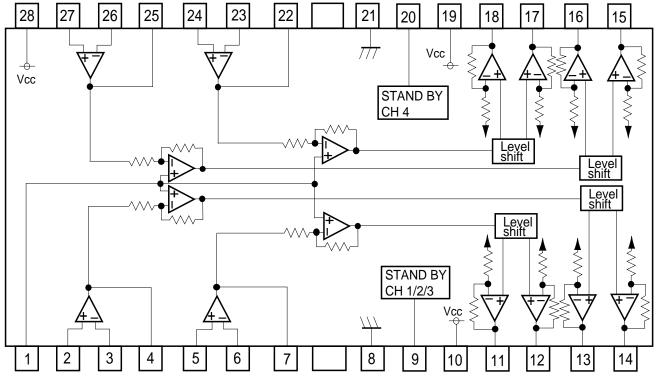

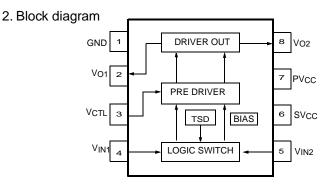

#### BA5983FM (DIC1) : Feed motor

1.Pin layout

2.Block diagram

#### 3.Pin function

| Pin No | Symbol         | I/O | Function                    | Pin No | Symbol  | I/O | Function                       |

|--------|----------------|-----|-----------------------------|--------|---------|-----|--------------------------------|

| 1      | <b>BIAS IN</b> |     | Input for Bias-amplifier    | 15     | VO4     | 0   | Non Inverted output of ch4     |

| 2      | OPIN           |     | Non inverting input for ch1 | 16     | VO4     | 0   | Inverted output of ch4         |

| 3      | OPIN           | I   | Inverting input for ch1     | 17     | VO3     | 0   | Non inverted output ch3        |

| 4      | OPOUT          | 0   | Output for ch1 op-amp       | 18     | VO3     | 0   | Inverted output of ch3         |

| 5      | OPIN2          | I   | Non inverting input for ch2 | 19     | PowVcc2 | -   | Vcc for ch3/4 power block      |

| 6      | OPIN2          | I   | Inverting input for ch2     | 20     | STBY2   |     | Input for ch4 stand by control |

| 7      | OPOUT2         | 0   | Output for fh2 op-amp       | 21     | GND     | -   | Substrate ground               |

| 8      | GND            | -   | Substrate ground            | 22     | OPOUT3  | 0   | Output for ch3 op-amp          |

| 9      | STBY1          | Ι   | Input for ch1/2/3           | 23     | OPIN3   | -   | Inverting input for ch3 op-amp |

| 10     | PowVcc1        | -   | Vcc for ch1/2 power block   | 24     | OPIN3   | I   | Non inverting input for ch3    |

| 11     | VO2            | 0   | Inverted output of ch2      | 25     | OPOUT4  | 0   | Output for ch4 op-amp          |

| 12     | VO2            | 0   | Non inverted output of ch2  | 26     | OPIN4   | I   | Inverting input for ch4 op-amp |

| 13     | VO1            | 0   | Inverted output of ch1      | 27     | OPIN4   | I   | Non inverting input for ch4    |

| 14     | VO1            | 0   | Non inverted output of ch1  | 28     | PreVcc  | -   | Vcc for pre block              |

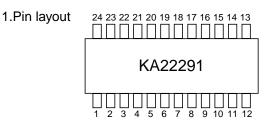

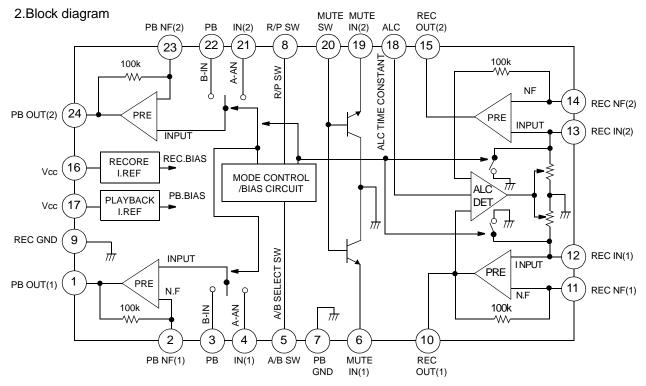

#### ■ KA22291 (JIC1) : PB/REC Pre. amp.

#### ■ FAN8082 (DIC2,DIC3) : DC motor driver

1.Pin layout

#### 3. Pin function

| Pin Number | Pin Name | I/O | Pin Function Description |

|------------|----------|-----|--------------------------|

| 1          | GND      | -   | Ground                   |

| 2          | VO1      | 0   | Output 1                 |

| 3          | VCTL     | I   | Motor speed control      |

| 4          | VIN1     | I   | Input 1                  |

| 5          | VIN2     | I   | Input 2                  |

| 6          | SVCC     | -   | Supply voltage (Signal)  |

| 7          | PVcc     | -   | Supply voltage (Power)   |

| 8          | VO2      | 0   | Output 2                 |

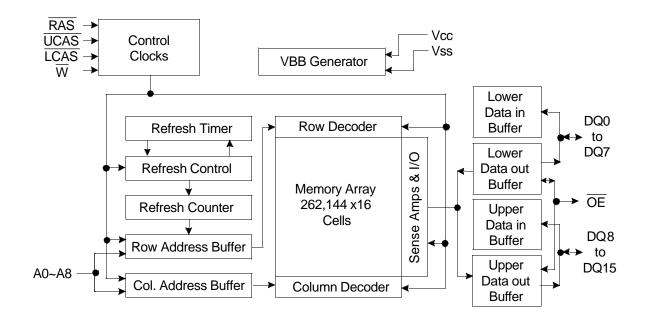

#### ■ 416C254 (SIC1) : CMOS DRAM

#### 1.Pin layout

| Vcc II<br>DQ0 II<br>DQ1 II<br>DQ2 II<br>DQ3 II<br>Vcc II<br>DQ4 II | 2<br>3<br>4<br>5<br>6 | 40 Vss<br>39 DQ15<br>38 DQ14<br>37 DQ13<br>36 DQ12<br>35 Vss<br>34 DQ11                      |

|--------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------|

| DQ5 L<br>DQ6 L<br>DQ7 L                                            | 8<br>9<br>10          | 33 🗖 DQ10<br>32 🗖 DQ9<br>31 🗖 DQ8                                                            |

| N.C.<br>N.C.<br>W<br>RAS<br>N.C.<br>A0<br>A1<br>A2<br>A3<br>Vcc    | 15                    | 30 N.C<br>29 LCAS<br>28 UCAS<br>27 OE<br>26 A8<br>25 A7<br>24 A6<br>23 A5<br>22 A4<br>21 Vss |

| Pin No. | Symbol  | I/O | Function                    |

|---------|---------|-----|-----------------------------|

| 16~19   | A0~A3   | I   | Address Inputs              |

| 22~26   | A4~A8   | I   | Address Inputs              |

| 2~5     | DQ0~3   | I/O | Data In/Out                 |

| 7~10    | DQ4~7   | I/O | Data In/Out                 |

| 31~34   | DQ8~11  | I/O | Data In/Out                 |

| 36~39   | DQ12~15 | I/O | Data In/Out                 |

| 35,40   | Vss     | -   | Ground                      |

| 14      | RAS     | I   | Row Address Strobe          |

| 28      | UCAS    | -   | Upper Column Address Strobe |

| 29      | LCAS    |     | Lower Column Address Strobe |

| 13      | W       | I   | Read/Write Input            |

| 27      | ŌĒ      | 0   | Data Output Enable          |

| 1,20    | Vcc     | -   | Power(+5V)                  |

|         |         | -   | Power(+3.3V)                |

| 11,12   | N.C     | -   | No Connection               |

#### 3. Block diagram

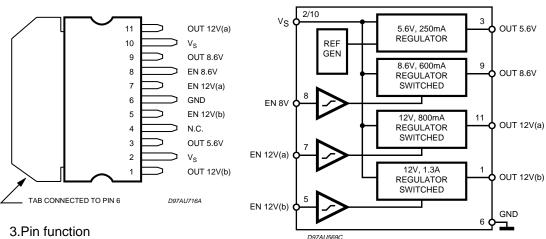

#### ■ L4959 (RIC1) : Voltage regulator

#### 1.Pin layout

2.Block diagram

#### 3.Pin function

| Pin No. | Symbol      | Function                                 |

|---------|-------------|------------------------------------------|

| 1       | OUT 12V (b) | 12V/1.3A SWITCHED OUTPUT VOLTAGE         |

| 2       | Vs          | Supply Voltage                           |

| 3       | OUT 5.6V    | 5.6V/250mA OUTPUT VOLTAGE                |

| 4       | N.C.        | not connected                            |

| 5       | EN 12V (b)  | Enable 12V/1.3A SWITCHED OUTPUT VOLTAGE  |

| 6       | GND         | Ground                                   |

| 7       | EN 12V (a)  | Enable 12V/0.8A SWITCHED OUTPUT VOLTAGE  |

| 8       | EN 8.6V     | Enable 8.6V/0.6A SWITCHED OUTPUT VOLTAGE |

| 9       | OUT 8.6     | 8.6V/0.6A SWITCHED OUTPUT VOLTAGE        |

| 10      | Vs          | Supply Voltage                           |

| 11      | OUT 12V (a) | 12V/0.8A SWITCHED OUTPUT VOLTAGE         |

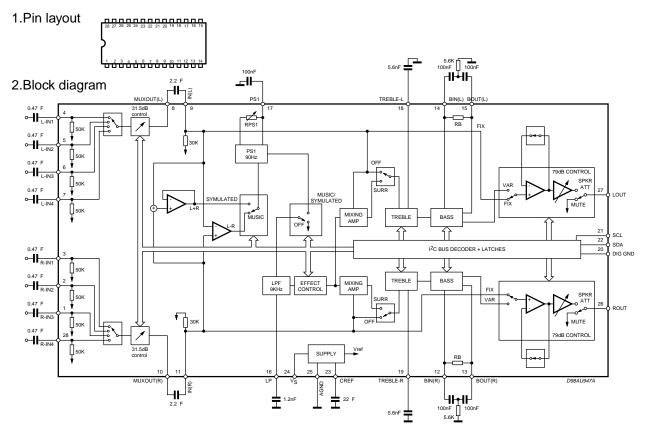

#### ■ TDA7442D (FIC1) : Audio processor

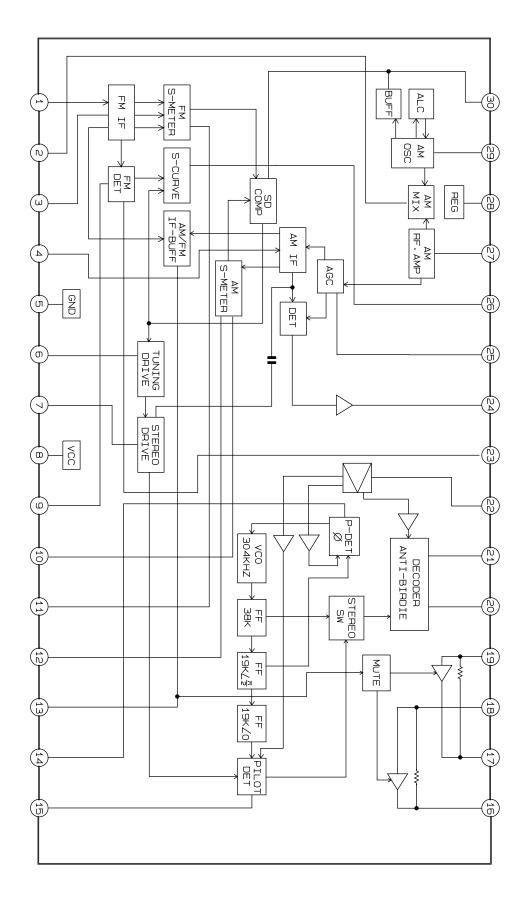

#### LA1837 (ICO1) : FM IF/DET AM RF/IF/DET

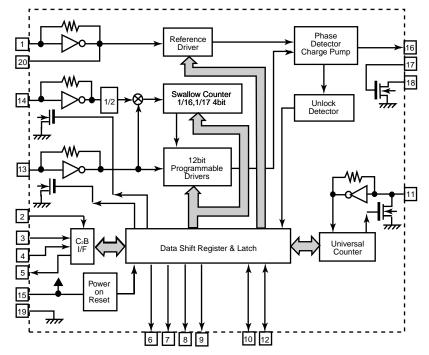

#### ■ LC72131M (ICO2) : PLL frequency synthesizer

1. Pin layout

| XIN<br>CE<br>DI<br>CL<br>DO<br>BO1<br>BO2<br>BO3<br>BO3 | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>0 | 20<br>19<br>18<br>17<br>16<br>15<br>14<br>13 | XOUT<br>Vss<br>AOUT<br>AIN<br>PD<br>VDD<br>FMIN<br>AMIN |

|---------------------------------------------------------|-------------------------------------------|----------------------------------------------|---------------------------------------------------------|

| BO3                                                     |                                           | 13                                           | <u>AM</u> IN                                            |

| <u>BO4</u>                                              | 9                                         | 12                                           | 102                                                     |

| 101                                                     | 10                                        | 11                                           | IFIN                                                    |

2. Block diagram

#### 3. Pin function

| Pin<br>No. | Symbol | I/O | Function                                 | Pin<br>No. | Symbol | I/O | Function                                 |

|------------|--------|-----|------------------------------------------|------------|--------|-----|------------------------------------------|

| 1          | XIN    | I   | X'tal oscillator connect (4.5MHz/7.2MHz) | 11         | IFIN   | I   | IF counter signal input                  |

| 2          | CE     | -   | Chip enable                              | 12         | IO2    | I/O | I/O port                                 |

| 3          | DI     | I   | Input data                               | 13         | AMIN   | I   | AM Local oscillator signal input         |

| 4          | CL     | I   | Clook                                    | 14         | FMIN   | I   | FM Local oscillator signal input         |

| 5          | DO     | 0   | Output data                              | 15         | VDD    | Ι   | Power suplly(VDD=4.5-5.5V)               |

| 6          | BO1    | 0   | Output port                              | 16         | PD     | 0   | Charge pump output                       |

| 7          | BO2    | 0   | Output port                              | 17         | AIN    | I   | Low-pass filter                          |

| 8          | BO3    | 0   | Output port                              | 18         | AOUT   | 0   | Amplifier Tr                             |

| 9          | BO4    | 0   | Output port                              | 19         | GND    | -   | Connected to GND                         |

| 10         | ĪO1    | I/O | I/O port                                 | 20         | XOUT   | I   | X'tal oscillator connect (4.5MHz/7.2MHz) |

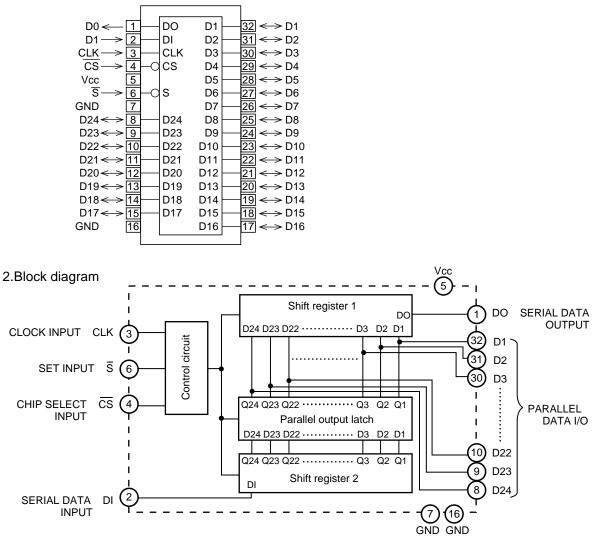

#### M66010 (UIC2) : I/O control

1.Pin layout

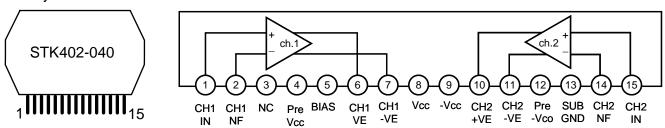

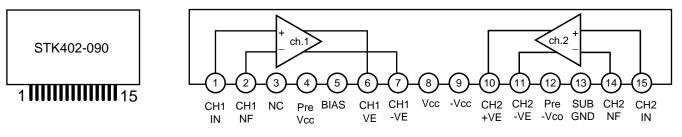

STK402-040 (AIC1) : 2channel AF power amp.

1.Pin layout

STK402-090 (AIC2) : 2channel AF power amp.

1.Pin layout

#### SP3721A (RIC1) : DVD driver

1.Pin layout

2.Pin Function (1/2)

| Pin No. | Symbol  | I/O | Function                                                                               |

|---------|---------|-----|----------------------------------------------------------------------------------------|

| 1       | DVDRFP  | 1   | RF Signal Inputs. Differential RF signal attenuator input pins.                        |

| 2       | DVDRFN  |     |                                                                                        |

| 3,4     | PD1,PD2 | 1   | CD Photo detector Interface Inputs. Inputs from the CD photo detector error outputs.   |

| 5~6     | A2,B2   | 1   | Photo Detector Interface Inputs. AC coupled inputs for the DPD from                    |

| 7~ 8    | C2,D2   |     | the main beam Photo detector matrix outputs.                                           |

| 9       | CP      | 1/0 | Differential Phase tracking LPF pin. An external capacitance is                        |

|         |         |     | connected between this pin and the CN pin.                                             |

| 10      | CN      | 1/0 | Differential Phase tracking LPF pin. An external capacitance is                        |

| _       |         |     | connected between this pin and the CP pin.                                             |

| 11~14   | A,B,C,D | 1   | Photo Detector Interface Inputs. Inputs from the main beam Photo                       |

|         | , , - , |     | detector matrix outputs.                                                               |

| 15~16   | E,F     |     | CD tracking Error Inputs. Inputs from the CD photo detector error outputs.             |

| 17      | CDTE    | -   | CD Tracking. E-F Opamp output for feedback.                                            |

| 18      | VCI2    | -   | Reference Voltage input. DC bias voltage input for the servo input reference.          |

| 19      | NC      | -   | No Connect.                                                                            |

| 20      | VNB     | -   | Ground. Ground pin for the servo block.                                                |

| 21      | DVDPD   | 1   | APC Input. DVD APC input pin from the monitor photo diode.                             |

| 22      | DVDLD   | 0   | APC output. DVD APC output pin to control the laser power.                             |

| 23      | CDPD    | I   | APC Input. DVD APC input pin from the monitor photo diode.                             |

| 24      | CDLD    | 0   | APC output. DVD APC output pin to control the laser power.                             |

| 25      | LDON#   | I   | APC output. on/off. APC output control pin. A low level activates the                  |

|         |         |     | LD output. (open high)                                                                 |

| 26      | VC      | -   | Reference Voltage output. This pin provides the internal DC bias                       |

|         |         |     | reference voltage (+2.5+ fix). Output impedance is less than 50 ohms.                  |

| 27      | VCI     | -   | Reference Voltage input. DC bias voltage input for the servo input reference.          |

| 28      | VPB     | -   | Power. Power supply pin for the servo block.                                           |

| 29      | MIRR    | 0   | Mirror Detect Output. Mirror Detect comparator output. Pseudo CMOS output.             |

| 30      | MP      | -   | MIRR signal Peak hold pin. An external capacitance is connected to                     |

|         |         |     | between this pin and VPB.                                                              |

| 31      | MB      | -   | MIRR signal Bottom hold pin. An external capacitance is connected to                   |

|         |         |     | between this pin and VPB.                                                              |

| 32      | FDCHG#  | I   | Low Impedance Enable. A TTL compatible input pin that activates the FDCHG switches.    |

|         |         |     | A low level activates the switches and the falling edge of the internal FDCHG triggers |

|         |         |     | the fast decay for the NIRR bottom hold circuit. (open high)                           |

| 33      | MLPF    | -   | MIRR signal LPF pin. An external capacitance is connected between this pin and VPB.    |

#### MX-DVA5

SP3721A

Pin Function (2/2)

| · · · · · | Function (2/2 | _/     |                                                                                        |

|-----------|---------------|--------|----------------------------------------------------------------------------------------|

| Pin No.   | Symbol        | I/O    | Function                                                                               |

| 34        | MEVO          | 0      | SIGO Bottom Envelope Output. Bottom envelope for Mirror detection.                     |

| 35        | MIN           | Ι      | RF signal Input for Mirror. AC coupled inputs for the mirror detection                 |

|           |               |        | circuit from the pull-in signal output. (PI)                                           |

| 36        | PI            | 0      | Pull-in Signal Output. The summing signal output of A,B,C,D or PD1,                    |

|           |               |        | PD2 for mirror detection. Reference to VCI.                                            |

| 37        | DFT           | 0      | Defect Output. Pseudo CMOS output. When a defect is detected, the                      |

|           |               |        | DFT output goes high. Also the servo AGC output can be monitored at                    |

|           |               |        | this pin, When CAR bits 7-4 are '0011'.                                                |

| 38        | TPH           | -      | PI Top Hold pin. An external capacitance is connected between this pin and VPB.        |

| 39        | MEV           | -      | SIGO Bottom Envelope pin. An external capacitance is connected                         |

|           |               |        | between this pin and VPB.                                                              |

| 40        | MEI           | 1      | Mirror Envelope Input. The SIGO envelope input pin.                                    |

| 41        | TE            | 0      | Tracking Error Signal Output. Tracking error output reference to VCI.                  |

| 42        | FE            | 0      | Focusing Error Signal Output. Focus error output reference to VCI.                     |

| 43        | CE            | 0      | Center Error Signal Output. Center error out put reference to VCI.                     |

| 43        | LCN           | -      | Center Error LPF pin. An external capacitance is connected between                     |

| 44        | LON           | -      | this pin and the LCP pin.                                                              |

| 45        | LCP           | -      | Center Error LPF pin. An external capacitance is connected between                     |

| 40        | LCF           | -      | this pin and the LCN pin.                                                              |

| 40        | 00114         |        | Serial Clock. Serial Clock CMOS input. The clock applied to this pin                   |

| 46        | SCLK          | I      |                                                                                        |

| 47        |               |        | is synchronized with the data applied to SDATA. (Not to be left open).                 |

| 47        | SDATA         | I/O    | Serial Data. Serial data bi-directional CMOS pin. NRZ programming                      |

|           | 0051          |        | data for the internal registers is applied to this input. (Not to be left open)        |

| 48        | SDEN          | I      | Serial Data Enable. Serial enable CMOS input. A high level input                       |

| 40        |               |        | enables the serial port. (Not to be left open)                                         |

| 49        | HOLD1         | Ι      | Hold Control. ATTL compatible control pin which, when pulled high, disables the RF AFC |

|           |               |        | charge pump and holds the RE AGC amplifier gain at its present value. (open high)      |

| 50        | VNA           | -      | Ground. Ground pin for the RF block and serial port.                                   |

| 51        | FNN           | 0      | Differential Normal Output. Filter normal outputs.                                     |

| 52        | FNP           | 0      | Differential Normal Output. Filter normal outputs.                                     |

| 53        | DIP           | I      | Analog inputs for RF Single Buffer. Differential analog inputs to the RF single-ended  |

|           |               |        | output buffer and full wave rectifier.                                                 |

| 54        | DIN           | I      | Analog inputs for RF Single Buffer. Differential analog inputs to the RF single-ended  |

|           |               |        | output buffer and full wave rectifier.                                                 |

| 55        | RX            | -      | Reference Resistor Input. An external 8.2 kohm, 1% resistor is                         |

|           |               |        | connected from this pin to ground to establish a precise PTAT                          |

|           |               |        | (proportional to absolute temperature) reference current for the filter.               |

| 56        | BYP           | I/O    | The RF AGC integration capacitor CBYP, is connected between BYP and VPA.               |

| 57        | SIGO          | 0      | Single Ended Normal Output. SIngle-ended RF output.                                    |

| 58        | VPA           | -      | Power. Power supply pin for the RF block and serial port.                              |

| 59        | AIP           | I      | AGC Amplifier Inputs. Differential AGC amplifier input pins.                           |

| 60        | AIN           | Ι      | AGC Amplifier Inputs. Differential AGC amplifier input pins.                           |

| 61        | ATON          | 0      | Differential Attenuator Output. Attenuator outputs.                                    |

| 62        | ATOP          | 0      | Differential Attenuator Output. Attenuator outputs.                                    |

| 63        | CDRF          | Ī      | RF Signal Input. Single-ended RF signal attenuator input pin.                          |

| 64        | CDRFDC        | 0      | CD RF Signal Output. Single ended CD RF summing output.                                |

|           | 0210100       | $\sim$ | 5 i 5 ···· 5 ····                                                                      |

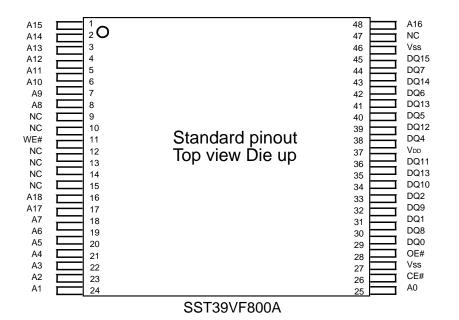

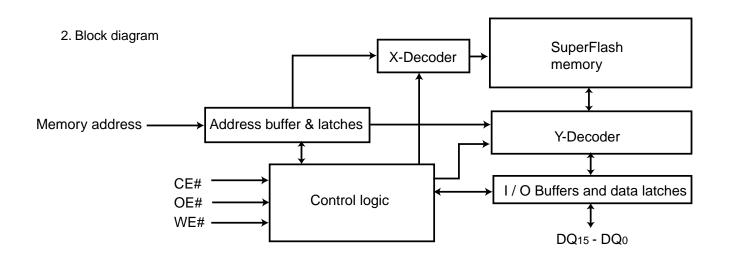

#### SST39VF800A (U6) : 8M bits malti-purpose flash

1.Pin layout

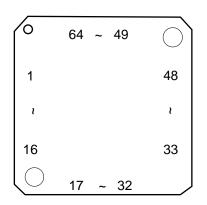

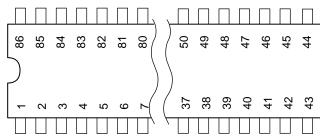

#### ■ W986432DH-7 (U5) : 32 Bits SDRAM

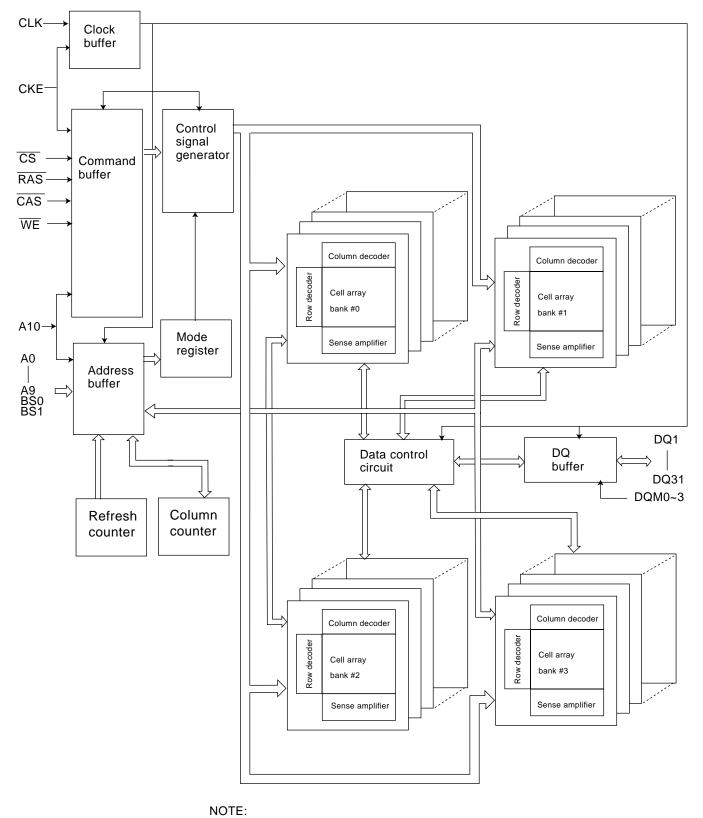

#### 1. Block diagram

The cell array configuration is 2048 \* 256 \* 32

2.Pin layout

3.Pin function

| Pin No. | I/O | Symbol  | Function                                                                  |

|---------|-----|---------|---------------------------------------------------------------------------|

| 1       | -   | Vcc     | Power for input buffers and logic circuit inside DRAM. (+3.3V)            |

| 2       | I/O | DQ0     | Multiplexed pins for data out put and input.                              |

| 3       | I/O | VccQ    | Separated power from VCC, to improve DQ noise immunity. (+3.3V)           |

| 4~5     | I/O | DQ1~DQ2 | Multiplexed pins for data out put and input.                              |

| 6       | I/O | VssQ    | Separated power from VSS, to improve DQ noise immunity.                   |

| 7~8     | I/O | DQ3~DQ4 | Multiplexed pins for data out put and input.                              |

| 9       | I/O | VccQ    | Separated power from VCC, to improve DQ noise immunity.                   |

| 10~11   | I/O | DQ5~DQ6 | Multiplexed pins for data out put and input.                              |

| 12      | I/O | VssQ    | Separated power from VSS, to improve DQ noise immunity.                   |

| 13      | I/O | DQ7     | Multiplexed pins for data out put and input.                              |

| 14      | -   | NC      | No connection                                                             |

| 15      | -   | Vcc     | Power for input buffers and logic circuit inside DRAM. (+3.3V)            |

| 16      | I/O | DQM0    | The output buffer is placed at Hi-Z (with latency of 2) when DQM is       |

|         |     |         | sampled high in read cycle. In write cycle, sampling DQM high will        |

|         |     |         | block the write operation with zero latency.                              |

| 17      | -   | WE      | Referred to RAS                                                           |

| 18      | -   | CAS     | Referred to RAS                                                           |

| 19      | -   | RAS     | Command input. When sampled at the rising edge of the clock RAS,          |

|         |     |         | $\overline{CAS}$ and $\overline{WE}$ define the operation to be executed. |

| 20      | -   | CS      | Disable or enable the command decoder. When command decoder is            |

|         |     |         | disabled, new command is ignored and previous operation continues.        |

| 21      | -   | NC      | No connection                                                             |

| 22~23   | -   | BS0     | Select bank to activate dining row address latch time,                    |

|         | -   | BS1     | or bank to read / write during address latch time.                        |

| 24~27   | -   | A0~A10  | Multiplexed pins for row and column address. Row address: Ao-A10.         |

|         |     |         | Column address:A0-A7.A10 is sampled during a recharge command to          |

|         |     |         | determine if all banks are to be recharged or bank selected by BS0, BS1.  |

| 28      | I/O | DQM2    | The output buffer is placed at Hi-Z (with latency of 2) when DQM is       |

|         |     |         | sampled high in read cycle. In write cycle, sampling DQM high will        |

|         |     |         | block the write operation with zero latency.                              |

| 29      | -   | Vcc     | Power for input buffers and logic circuit inside DRAM. (+3.3V)            |

| 30      | -   | NC      | No connection                                                             |

| 31      | I/O | DQ16    | Multiplexed pins for data out put and input.                              |

| 32      | I/O | VssQ    | Separated power from VSS, to improve DQ noise immunity.                   |

| 33~34   | I/O | DQ17~18 | Multiplexed pins for data out put and input.                              |

| 35      | I/O | VssQ    | Separated power from VCC, to improve DQ noise immunity.                   |

| Pin No. | I/O | Symbol  | Function                                                                 |

|---------|-----|---------|--------------------------------------------------------------------------|

| 36~37   | I/O | DQ19~20 | Multiplexed pins for data out put and input.                             |

| 38      | I/O | VssQ    | Separated power from VSS, to improve DQ noise immunity.                  |

| 39~40   | I/O | DQ21~22 | Multiplexed pins for data out put and input.                             |

| 41      | -   | VccQ    | Separated power from VCC, to improve DQ noise immunity. (+3.3V)          |

| 42      | I/O | DQ23    | Multiplexed pins for data out put and input.                             |

| 43      | -   | Vcc     | Power for input buffers and logic circuit inside DRAM. (+3.3V)           |

| 44      | -   | Vss     | Ground for input buffers and logic circuit inside DRAM.                  |

| 45      | I/O | DQ24    | Multiplexed pins for data out put and input.                             |

| 46      | I/O | VssQ    | Separated power from VSS, to improve DQ noise immunity.                  |

| 47~48   | I/O | DQ25~26 | Multiplexed pins for data out put and input.                             |

| 49      | -   | VccQ    | Separated power from VCC, to improve DQ noise immunity. (+3.3V)          |

| 50~51   | I/O | DQ27~28 | Multiplexed pins for data out put and input.                             |

| 52      | I/O | VssQ    | Separated power from VSS, to improve DQ noise immunity.                  |

| 53~54   | I/O | DQ29~30 | Multiplexed pins for data out put and input.                             |

| 55      | -   | VccQ    | Separated power from VCC, to improve DQ noise immunity. (+3.3V)          |

| 56      | I/O | DQ31    | Multiplexed pins for data out put and input.                             |

| 57      | -   | NC      | No connection                                                            |

| 58      | -   | Vss     | Ground for input buffers and logic circuit inside DRAM.                  |

| 59      | I/O | DQM3    | The output buffer is placed at Hi-Z (with latency of 2) when DQM is      |

|         |     |         | sampled high in read cycle. In write cycle, sampling DQM high will       |

|         |     |         | block the write operation with zero latency.                             |

| 60~66   | -   | A3~A9   | Multiplexed pins for row and column address. Row address: Ao-A10.        |

|         |     |         | Column address:A0-A7.A10 is sampled during a recharge command to         |

|         |     |         | determine if all banks are to be recharged or bank selected by BS0, BS1. |

| 67      | -   | CKE     | CKE controls the clock activation and deactivation.                      |

|         |     |         | When CKE is low, Power Down rising edge of clock.                        |

| 68      |     | CLK     | System clock used to sample inputs on the rising edge of clock.          |

| 69~70   | -   | NC      | No connection                                                            |

| 71      | I/O | DQM1    | The output buffer is placed at Hi-Z (with latency of 2) when DQM is      |

|         |     |         | sampled high in read cycle. In write cycle, sampling DQM high will       |

|         |     |         | block the write operation with zero latency.                             |

| 72      | -   | Vss     | Ground for input buffers and logic circuit inside DRAM.                  |

| 73      | I/O | NC      | No connection                                                            |

| 74      | I/O | DQ8     | Multiplexed pins for data out put and input.                             |

| 75      | I/O | VccQ    | Separated power from VCC, to improve DQ noise immunity. (+3.3V)          |

| 76~77   | I/O | DQ9~10  | Multiplexed pins for data out put and input.                             |

| 78      | I/O | VssQ    | Separated power from VSS, to improve DQ noise immunity.                  |

| 79~80   | I/O | DQ11~12 | Multiplexed pins for data out put and input.                             |

| 81      | I/O | VccQ    | Separated power from VCC, to improve DQ noise immunity. (+3.3V)          |

| 82~83   | I/O | DQ13~14 | Multiplexed pins for data out put and input.                             |

| 84      | I/O | VssQ    | Separated power from VSS, to improve DQ noise immunity.                  |

| 85      | I/O | DQ15    | Multiplexed pins for data out put and input.                             |

| 86      | 1   | Vss     | Ground for input buffers and logic circuit inside DRAM.                  |